(Part 5 of this series is here: Part 5)

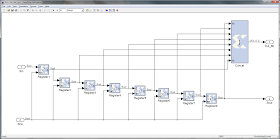

But before I begin, let me again acknowledge Dick Benson, W1QG. Dick is the father of this design, and although I've made some modifications to the FPGA logic, the underlying FPGA architecture and the vast majority of the Simulink implementation is Dick's.

A note regarding the schematics...

These schematics were drawn using the Lite version of Cadence's Orcad Capture. This is the free version of the program, and it limits a schematic's number of nets to 75 and the number of parts to 60 (limitations which apply if you want to save the design, which I always do).

Because this radio design has many more nets and parts than the 75/60 limit specified by Cadence, I have broken the overall design into smaller "bite size" schematics, each independent of the others and each drawn on a single A-size sheet.

But because I've broken up the design into smaller independent pieces, I can not use Capture's Design Rule Checker to check the overall design for design flaws. Therefore, there is the possibility that errors have crept into the schematics. So be aware!

A Note on Logic Levels:

A number of different logic families and devices are used in this radio. I want to ensure that input logic thresholds and output logic drive levels are compatible with each other. The spreadsheet below summarizes the different specifications:

Notes on Logic Levels:

Now, let's look at the overall Block Diagram of the FPGA SDR radio...

FPGA SDR Block Diagram:

The Main Board, which is the subject of this blog post, incorporates the FPGA, RF ADC, RF DAC, Audio Codec, Speaker Amplifier, and various miscellaneous support and interface circuits. It is the processing heart of the radio.

Notes on this block diagram:

Block Diagram, Main Board:

And below are some pictures of the Main Board in its Rev. A implementation:

And now, let's discuss the Main Board's hardware....

These schematics were drawn using the Lite version of Cadence's Orcad Capture. This is the free version of the program, and it limits a schematic's number of nets to 75 and the number of parts to 60 (limitations which apply if you want to save the design, which I always do).

Because this radio design has many more nets and parts than the 75/60 limit specified by Cadence, I have broken the overall design into smaller "bite size" schematics, each independent of the others and each drawn on a single A-size sheet.

But because I've broken up the design into smaller independent pieces, I can not use Capture's Design Rule Checker to check the overall design for design flaws. Therefore, there is the possibility that errors have crept into the schematics. So be aware!

A Note on Logic Levels:

A number of different logic families and devices are used in this radio. I want to ensure that input logic thresholds and output logic drive levels are compatible with each other. The spreadsheet below summarizes the different specifications:

(Click on image to enlarge)

Notes on Logic Levels:

- The Xilinx output voltages aren't high enough to meet the worst-case Arduino Input Level specification, so their levels will need to be shifted if driving Arduino inputs (this level-shifting is done in the Front Panel circuitry).

- 2N7000 devices make for simple I/O drivers (e.g. relay drivers, etc.) But their worst-case Vgs is 3V. This value is sufficient when driven with output levels from 5V devices (e.g. Arduino), but it is above worst-case Xilinx drive levels. For this reason I will use bipolar transistors (rather than 2N7000 transistors) for I/O interfacing, when needed.

- The 74VCX245 transceiver is the output driver for the LTC DC918C ADC demo board. It is powered by 2.5 VDC, and its outputs drive the Xilinx FPGA.

Now, let's look at the overall Block Diagram of the FPGA SDR radio...

FPGA SDR Block Diagram:

(Click on image to enlarge)

The Main Board, which is the subject of this blog post, incorporates the FPGA, RF ADC, RF DAC, Audio Codec, Speaker Amplifier, and various miscellaneous support and interface circuits. It is the processing heart of the radio.

Notes on this block diagram:

- The T/R relay, when un-energized (OFF), shorts the receiver's input to ground, protecting the receiver input circuitry when the radio is off.

- Various interfaces are shown to external devices. These interfaces will be explained further, below.

- All other circuitry not ON the Main Board will be described in future blog posts.

- Schematics and circuitry might change, as determined by design checkout.

Block Diagram, Main Board:

(Click on image to enlarge)

And below are some pictures of the Main Board in its Rev. A implementation:

Top Side

Bottom Side

And now, let's discuss the Main Board's hardware....

Hardware Design, Main Board:

Schematic, ADC Input:

(Click on image to enlarge)

Notes on ADC Input schematic:

- This radio uses a Linear Technology Demo Board (the DC918C, version C, incorporating an 80 MHz, 16-bit LTC2206 ADC) for the RF ADC.

- The DC918C's output drivers are 74LVX245 Buffers whose VCC is 2.46 volts (via an LT1763 LDO regulator). Therefore, the maximum high-level voltage from the board to the Xilinx inputs is about 2.26 volts (assuming 100uA worse-case output current -- this voltage falls as output current increases). With drive current at about 6 mA, the output voltage level is just within Xilinx input threshold specification, with the margin vanishingly small if using the Xilinx LVCMOS33 spec, but better with the LVCMOS25 spec.

- 12 VDC power comes in to the radio on this page. It is converted down to 5V using a simple LM2576 buck regulator, and it is this 5V power buss which sources power for the 3.3V LDO regulators used throughout this design.

(Click on image to enlarge)

Notes on the DC918C ADC Demo Board:

- Dick and I use the DC918C-C version of the DC918C Demo Board (80 MHz LTC2206). No modifications were made to this board.

- Schematics and other design files for the DC918C-C board can be found at the Linear Technology site: http://www.linear.com/solutions/3274

- LTC2206 Documentation can be found here: http://www.linear.com/product/LTC2206

- The DC918C-C's on-board jumpers are set as follows:

- JP1: Set to GND, not OVP.

- JP2 (SENSE): Set to VDD, not OPEN.

- JP3 (PGA): Set to VDD, not GND.

- JP4 (RAND): Set to GND, not VDD.

- JP5 (SHDN): Set to GND, not VDD.

- JP6 (DITH): Set to GND, not VDD.

Schematic, Clock and Misc.:

(Click on image to enlarge)

Notes on Clock and Misc.:

- The 80 MHz clock source is a Conner-Winfield TCXO (available from Digikey), part number TB522-080.0M. (LVCMOS outputs, 3.3Vdc).

- This TCXO drives a 74AC04 inverter whose input has been biased to mid-scale DC (1.65V) and which is AC-coupled to the TXCO output. This inverter, in turn drives other 'AC04 inverters which act as clock drivers, so that the FPGA clock, the ADC clock, and the DAC clock are driven independently. Thus, there is no clock daisy-chaining.

- R11 and R10 slightly roll off the clock edges to reduce ringing.

- J1 is the 26-pin header to connect the radio's Front Panel to the Main Board.

- Note that because the Front Panel's Arduino's output levels are referenced to the Arduino's 5V power, R5 and R6 drop the Arduino output voltages down to a level more compatible with the Xilinx input levels.

- R9 and C14 filter (and scale) the S-Meter PWM signal. Note that the meter is 1mA Full Scale.

- Q1 (open-collector inverter) can be used by the Front Panel (Arduino) to Reset the FPGA. For example, this is used if the Command Interface gets out of sync.

- The oscillator and 74AC04 are powered by the same 3.3V regulator used to power the LTC 918C-C ADC board. (This regulator also powers the Audio Codec).

Schematic, Xilinx FPGA Board:

(Click on image to enlarge)

Notes on Xilinx FPGA Board:

- Dick and I use a Waveshare Core3S500E Xilinx Development Board to simplify the FPGA hardware implementation (no need to solder an FPGA!).

- This schematic page defines which pins of the Waveshare Core3S500E board are used in this radio.

- I disabled the on-board 50 MHz oscillator by grounding its output-enable pin (pin 1), thus allowing the external 80 MHz clock to be connected to this oscillator's pin 3. (Note that pin 1 in the Waveshore partial-schematic, below, is simply called "NC". It actually is the oscillator's OE pin.)

- FPGA outputs TX_ATTEN_0 and TX_ATTEN_1 are not yet used in the design. I've included them in case I would like some way to change TX gain apart from adjusting the TX_Level within the FPGA. For example, these two bits could select different values for the DAC's full-scale current resistor.

- My modifications to this board are described below:

(Click on image to enlarge)

Notes on Mods to the Waveshare Core3S500E:

- Additional information on the Waveshare Core3S500E board can be found here: http://www.waveshare.com/wiki/Core3S500E

Schematic, DAC Out:

(Click on image to enlarge)

Notes on DAC Output:

- The DAC is an AD9744 14-bid ADC

- I use a separate 3.3V regulator for the DAC (to minimize possible noise injection into the DAC via its VCC pin if this regulator were also powering other devices).

- R1 sets the full-scale output current. With 2K ohms, full-scale current is 19.2 mA +/-5%, assuming R1 is 1%, given the spec'd range of VREFIO.

- IFS = 32*VREFIO/R1 = 32*1.2/R1.

Schematic, Audio Codec:

(Click on image to enlarge)

Notes on Audio Codec:

- The Audio Codec is an AKM AK4554 16-bit stereo audio codec.

- FPGA outputs driving this Codec are lightly filtered (e.g. R4/C17), to round off edges and thus lower harmonic energy (just in case they might be picked up by the receiver). Note -- strictly speaking, these 1-pole filters might not be needed in this design, but I got into the habit of using them long ago to help ensure that products I designed met EN61000 EMC standards. You'll see me use this technique throughout this design.

- All inputs (or outputs) to/from the outside world (e.g. Mic In, Line In, and Codec Right Out) are protected with TVS devices and series-resistors at the inputs (the latter to limit transient current).

- The Codec left-channel output first drives a low-pass filter (four-pole, cutoff at 4.9 KHz, gain of 1) which is between it and the input of the Speaker Amplifier.

- R1 (33K) sets the voltage gain of U2 (the Speaker Amplifier, a TPA0211 device) to 3.8 (= 125K/33K), which ensures that at the maximum Codec output (1.98 Vpp), the amplifier's drive into a 4-ohm speaker load will be about 1.8 watts RMS -- just below 2 watts, above which amplifier distortion increases significantly, per the TPA0211 datasheet.

- I jumper J5 pin 3 to J5 pin 4 (I am not using the originally planned-for functionality of J5).

- The primary function of C11 (510 pF) is to shunt RF (to hopefully minimize RF susceptibility).

- This design originally used a TI PCM3008 codec. But the TI codec has greater out-of-band noise compared to the AK4554 (which is pin-for-pin compatible with the PCM3008), as the following image demonstrates:

(Click on image to enlarge)

Schematics, Codec Four-Pole Lowpass Filter:

(Click on image to enlarge)

Notes on Codec Four-Pole Lowpass Filter:

- Two op-amp, four pole Sallen-Key Lowpass Filter (Fc = 4.9 KHz, Av = 1). I used this website: http://www.daycounter.com/Filters/Sallen-Key-LP-Calculator.phtml

- Because the LMC662 op-amps are powered only by a positive voltage, the input signal must have a DC offset. This offset is provided by the AK4554 codec (offset at 1/2 of VDD, or 1.65 VDC for a VDD of 3.3V). (Note that the max codec output, given a VDD or 3.3V, will be 1.98 Vpp for a typical AK4554).

- The LMC662 is powered by 12V (rather than 5V), because worst-case Common-Mode input range (V+ - 2.4V for the LMC662C), coupled with worst-case codec output positive swing (2.18 V, max) could have been an issue if the LMC662 had been powered with 5V (admittedly, it is an issue by only 0.08V, but given that 12V was readily available (actually, 14.5 VDC) , why not use that?).

- Here is a plot of the LPF's measured frequency response:

(Click on image to enlarge)

Schematic, Interconnects 1:

(Click on image to enlarge)

Notes on Interconnects 1:

- A separate 3.3V regulator is used to power the board's various interface circuitry (on this schematic page and the next 3 "Interconnects" pages).

- External I/O: EXT. IN and EXT. OUT usage is yet to-be-defined. I've included this I/O in the design "just in case" I find a need for it later.

- EXT_IN should not be driven higher than 3.3V -- TVS1 will protect it from over-voltage (current-limited by R7). And in the event of a large, positive-going transient event, D7 should prevent Q2's base-emitter junction from being damaged by an accidentally high reverse-bias Vbe voltage. (And note that EXT. IN will source power (3.3V dropped by Q2's Vbe, D2, and R7, so must ensure that devices attached to this pin will not be harmed by this current when they are powered off).

- Controls for an external Receive Attenuator are included. This attenuator might be a Mini-Circuits DAT-31A-SP+ Digital Attenuator, but it could be something else, as long as I can set attenuation with 3 bits.

- I've included an EXT. PA T/R relay-closure output for controlling external power amplifiers such as my SB-220 or AL-811.

Schematic, Interconnects 2:

(Click on image to enlarge)

Notes on Interconnects 2:

- This page contains an interface for communicating with my Automatic Antenna Tuner. This is a bit like putting the cart before the horse, because I don't have a corresponding interface in the Tuner. Never the less, someday there might be one! And in anticipation of that event I thought I'd add the circuitry here. (Note: the interface has since been implemented! See part 11 of this blog series).

- The Interface is pretty much self explanatory. The signals to the outside world have TVS with current-limiting resistors for over-voltage protection. And RF bypassing with small caps.

- Also, output filtering for three FPGA outputs is shown on this page -- these three filters were originally on the FPGA schematic page, but their inclusion there meant that the schematic exceeded the Orcad Lite's limits on nets/parts, so I moved them here.

Schematic, Interconnects 3:

(Click on image to enlarge)

Notes on Interconnects 3:

- I hope to incorporate a Flex-radio SDR-1000 PA module that I have into this radio to give it 100 watts out. Details are sketchy at the moment -- this PA might be mounted inside this radio's chassis, or it might be mounted in a separate case (so that it could be used for other purposes when not used for this radio. The important point is -- nothing is yet finalized! If the PA ends up in a separate case, I will probably use a 25-pin D-connector to connect that chassis to this radio -- using ribbon cable between the two units with ground between each signal will help reduce EMI susceptibility. Thus, the reason for J3.

- Assuming the SDR-1000 PA performs as I hope it will, I will describe in a later post how it connects to this radio.

- Open-collector drivers communicating between this radio and the PA provide a very simple interface between boards with different logic voltages (e.g. the radio's 3.3V digital power versus the PA's 5V digital power) -- no level-shifting required.

- ESD protection of the signals driven by the ULN2003A is provided, for positive-going pulses, by TVS2, connected to U1's internal clamping diodes. Although I've never tried ESD protection this way, it seems to me it should work, and it saves parts, as I don't need a TVS device for each line. Negative-going pulses are clamped by internal clamp diodes (within the ULN2003) between the output pins and ground.

Schematic, Interconnects 4:

(Click on image to enlarge)

Notes on Interconnects 4:

- A future project of mine is a 500 watt external PA. This interface would allow the FPGA SDR radio to set automatically the PA's output filters, etc. Note this interface's similarity to the SDR-1000 interface, above.

- I've added an extra PA Filter-selection signal (nFilt_F3), in case I need to specify separate, rather than combined, filters (e.g. the SDR-1000 PA combines 10 and 12 meters into a common filter, but I might find that I need to separate these filters into two separate filters, rather than one combined filter, in the 500 watt PA).

- Due to Orcad Lite's net and part limitations, the SW1 and SW2 are shown on this page rather than on the FPGA page.

Construction Notes:

This board was built on a piece of scrap double-sided FR4 PCB stock. Very handy, and it provides an excellent ground plane. I cut holes in it to mount the FPGA board so that I could easily access both sides of this board, as well as to mount an Electroboard prototyping board with the AD9744 DAC soldered to it. (I also use one of their prototyping boards to mount the PCM3008 codec, but I did not cut a hole into the main board -- instead, this prototyping board is soldered to the top ground plane of the main board).

For mounting small parts, I often used small rectangles I had cut from a larger BusBoard Prototyping Systems prototyping board. These are great for mounting small SMD devices, relays, and even ULN2003A DIP ICs.

And at times I also carved pads out of the copper plane on either side of the main PCB (depending upon which side it made sense to mount the components), using a Dremel tool and a 30 degree, 0.1mm Tip Diameter Conical Engravers Cutter V-bit. You can see an example of this, above, for the 3.3V LDO regulator used to power the interface circuitry.

That's it for this blog post!

Background Notes:

SDR Notes: Weaver Modulation and Demodulation

SDR Notes: The Mixer Mathematics of Digital Down Conversion

Posts in this Series:

Part 1: Overview

Part 2: FPGA Modulation and Demodulation

Part 3: Interpolation and Decimation Filters

Part 5: Control Interface, Etc.

Part 9: 50 dB HF RF Power Amplifier

Standard Caveat:

I or Dick might have made a mistake in our designs, equations, schematics, models, etc. If anything looks confusing or wrong to you, please feel free to comment below or send me an email.

Also, I will note:

This design and any associated information is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE.