(Part 8 of the series is here: Part 8).

The HF RF PA is shown above, below the K6JCA FPGA SDR transceiver.

Before I begin, let me again acknowledge Dick Benson, W1QG. Dick is the father of this FPGA SDR design, and although I've made some modifications to the FPGA logic, the underlying architecture and the vast majority of the Simulink implementation is Dick's.

These schematics were drawn using the Lite version of Cadence's Orcad Capture. This is the free version of the program, and it limits a schematic's number of nets to 75 and the number of parts to 60 (limitations which apply if you want to save the design, which I always do).

Because this radio design has many more nets and parts than the 75/60 limit specified by Cadence, I have broken the overall design into smaller "bite size" schematics, each independent of the others and each drawn on a single A-size sheet.

But because I've broken up the design into smaller independent pieces, I can not use Capture's Design Rule Checker to check the overall design for design flaws. Therefore, there is the possibility that errors have crept into the schematics. So be aware!

Note: This Post in a Work in Progress and thus

Not Yet Finished!

PA voltage is 14 VDC (or, if one prefers, 13.8 VDC).

You might be wondering -- why did I install the 30 dB driver stage in this amplifier chassis and not in the FPGA SDR transceiver chassis?

The main reason is: control of the 30 dB driver's load impedance. The SDR-1000 PA's input impedance is not 50 ohms (at least, not on the higher bands). Thus, if there is a length of 50 ohm coax between the driver's output and the SDR-1000 PA input, the 30 dB Driver's load impedance will change as a function of coax length.

So, I thought it better to have this length of coax be fixed, rather than be some unknown length, so that system performance would not vary depending upon whatever random length of coax I might happen to use to connect the FPGA SDR transceiver to the PA, if the 30 dB driver were in the transceiver rather than PA chassis.

Block Diagram:

(Click on image to enlarge)

Notes on Block Diagram:

- 50 dB of amplification is achieved with a 30 dB Driver followed by a 20 dB PA.

- The 20 dB PA is an SDR-1000 PA Module (Flexradio transceiver).

- The FPGA SDR transceiver controls the driver and SDR-1000 PA module via an 8-wire (plus shield) parallel interface, implemented with an RJ-45 connector. This interface selects the appropriate band-specific low-pass output filter and also carries the T/R signal.

- The 30 dB driver is switched in-line during transmit. During receive this driver is bypassed, and the RF In and RF Out connectors are connected together without any amplification or filtering in-line -- the receive signal pass directly from the "RF Out" connector to the "RF In" connector (and to the FPGA SDR) without modification.

- 14VDC from the rear panel goes directly to the SDR-1000 PA, where it is fused (25A fuse). Following this fuse the 14V can power external devices (such as the FPGA SDR) as well as internal circuitry within the PA chassis.

Schematics:

Back Panel Schematic:

(Click on image to enlarge)

Notes on Back Panel Schematic:

- Several connectors are not used (at this time), but have been installed in anticipation of their incorporation.

- At the moment, the fan voltage is set to about 7 volts (via the resistors) to ensure that it isn't too loud. In the future I would like to add a temperature sensor (to the PA heatsink) and use that sensor's output to control the fan's speed.

RJ-45 Control Interface Schematic:

The FPGA SDR controls the HF RF PA via a parallel interface, implemented with an 8-pin shielded RJ-45 connector:

(Click on image to enlarge)

Notes on RJ-45 Control Interface Schematic:

- The RJ-45 cable must be shielded, as this shield carries the ground-return for the control signals.

- All 8 wires are connected, although only 7 are used to carry signaling at this time. (The unused eighth wire is there in case I need to add additional functionality in the future -- for example, if, for some reason, I need to differentiate between between bands that, in the SDR-1000 PA implementation, are paired to share a common low-pass filter at the PA output (e.g. the band-pairs 60/40, 30/20, 17/15, and 12/10 meters).

- All control signals have simple 1-pole RC low-pass filters to help block external RF from the internal circuitry. ESD control is also handled with 5V TVS devices (note that the R in the RC filters will current-limit ESD hits on any line). ESD protection isn't really required in a "one-off" design, but adding such protection was required in a number of commercial products that I designed. I believe it is a good design habit to have, and I've carried this practice forward into my personal designs.

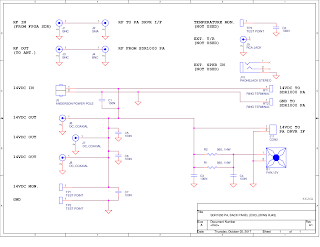

PA Interface Schematic:

The PA Interface provides the necessary circuitry to allow the RJ-45 interface signals (from the FPGA SDR) to control the PA and PA Driver. It also provides an interface for internal control to allow this amplifier to be used in stand-alone applications -- control would be handled via front-panel switches (i.e. selecting low-pass filters) and an external T/R input on the back panel -- but note that, at this time, "internal control" of the amplifier has not been implemented.

(Click on image to enlarge)

Notes on PA Interface Schematic:

- The "External Control" connector attaches to the RJ-45 Interface (see earlier schematic) via a 16-pin cable, and it is the port through which the FPGA SDR controls the PA.

- The "Internal Control" connector can connect "local" (front-panel) controls to the PA and thus could allow the amplifier to be used in stand-alone applications without the FPGA SDR transceiver being attached to its "External Control" interface. (At the moment, though, there are no "local" controls).

- Given that there are no "local" controls at this moment, J16 should be shorted -- this signal, when low, tells the FPGA SDR transceiver that it is connected to the PA. (If there were local controls, this signal would be forced high if the PA were placed in "local" mode, rather than in "FPGA SDR" Control mode).

- The nPA_EN signal at J8 is not used -- I had intended to have the FPGA SDR drive this signal, to turn ON the bias regulator on the SDR-1000 PA Module (via J5 pin 9), but there was too much current, and thus too much voltage drop, through the various 100 ohm resistors in my EMI-mitigation low-pass filters that I decided to remove this function. Instead, J5 pin 9 now connects to the drain of Q8, a 2N7000 that, during Transmit, pulls J5 pin 9 low and turns ON the PA bias. Header J18 is there in case I want to force the PA Bias to be ON (by shorting the two header pins).

- At J5, the PAF0 - PAF2 bits select the SDR-1000 PA module's output lowpass filter (per the table shown on the schematic page), while PATR is the T/R signal (high = transmit). These signals are driven by a ULN2003 IC in the SDR FPGA radio -- an open collector driver which inverts them from their "high-true" sense, and these signals are inverted here again (back to their original sense) using 2N3905 PNP transistors. Bypass caps across the transistors' base-emitter junctions, as well as from the collectors to ground, to shunt RF off of these lines (or junctions) and thus help mitigate any issues caused by RF pickup.

- At J8, nEXT_CTRL is meant to allow the FPGA SDR transceiver to force the PA into "FPGA SDR" control mode, if it had been set to "local" control mode via the PA's (currently non-existent) front panel controls.

- At J7, nDRVR_BYPASS is meant to allow the 30 dB Driver stage to be bypassed (when in "local" control mode), in case this PA were to be used in a stand-alone application for which that extra 30 dB of drive was not needed -- for example, to amplify a 1 watt QRP transceiver's output.

- At the moment the 5V connector, J17, is not used. It is there to power any "Internal Control" circuitry that I might want to add to this design in the future.

- I'm not using the FlexRadio PA's directional coupler (with its on-board ADC), so the three control pins for this ADC (located at J5, pins 4, 5, and 6) are all pulled HIGH.

PA Driver Interface Schematic:

The PA Driver Interface switches the PA Driver into and out of the signal path. During transmit it is in the signal path, and during receive it is bypassed.

(Click on image to enlarge)

Notes on PA Driver Interface Schematic:

- The PA Driver (discussed below) is powered by 12 VDC (the OPA2674's "Absolute Maximum" power supply rating is 13.0 VDC) , and I use an LM2940 low-dropout regulator (LDO) to create 12 volts from the 14 volts used to power the PA. But note that this LDO is actually mounted on the PA Driver board heatsink, not on the PA Driver Interface board.

- LDO regulators can suffer from loop instability and usually require that the ESR of their output capacitor(s) be within a certain range (refer to section 8.2.2.1.2 in the LM2940 datasheet). I'm using a Kemet T491D476M016AT 47uF, 16V, Tantalum cap, whose ESR is spec'd at 800 milliohms.

- 1N4148 diodes clamp the back-voltage across each relay coil when that coil is "released".

PA Driver Schematic:

The PA Driver provides 30 dB (or so) of low-distortion amplification of the FPGA SDR's 0 dBm output signal.

(Click on image to enlarge)

Notes on PA Driver Schematic:

- The PA Driver is based upon the driver in the HPSDR Pennylane board, designed by Phil Harman (VK6APH) and Lyle Johnson (KK7P). Link to the Pennylane schematics: https://openhpsdr.org/wiki/images/3/31/Pennylanea1.pdf.

- Refer to the other notes my schematic, above.

Front Panel Schematic:

The front panel is simplicity itself and consists only of two LEDs. A green LED illuminates when the PA is powered up, and a red LED illuminates during Transmit.

(Click on image to enlarge)

(No notes on the Front Panel Schematic.)

FlexRadio SDR-1000 PA Mods:

While testing the PA Module in my chassis I discovered that the FlexRadio PA's LPF-select relays would chatter (or erroneously turn ON) on some bands, at some power levels.

To help quench this RFI issue, I stiffened up the filtering on the three PAF bits (used to select the LPF to be used for a specific band) by paralleling the existing 10 NF caps with 100 NF caps. (These signals can be heavily loaded with capacitance because their timing is not critical -- they only change when the user selects a new band).

The modification is shown, below.

(Click on image to enlarge)

Implementation:

I built the PA into an old HP 37203A HP-IB Extender chassis (this is the same type of chassis that I used for the FPGA SDR transceiver).

Top View:

Notes on Overall Implementation:

- The PA Interface board and the SDR-1000 PA Module are mounted on a piece of PCB copper-clad board that serves as a bottom mounting plate.

- The PA Driver and PA Driver Interface are mounted to the side of the chassis.

Driver and Driver Interface:

Notes on Driver and Driver Interface Implementation:

- The LM2940 LDO is at the left of the picture above, soldered to a copper sheet used as a heatsink.

- The copper sheet also bends up and is soldered to the PA Driver board -- several pennies are soldered to the copper plane on the backside of the Driver board (under the OPA2674 drivers) to conduct heat from the back of the board. The copper sheet is soldered to the other side of these pennies. Thus, heat is conducted from the back side of the driver board, through the pennies, and to the copper sheet which is screwed to the HP chassis side rails. (Note that pre-1982 pennies have a much higher copper content than later pennies, and thus I prefer them for their heat transfer characteristics).

Back Panel:

(No notes on the back panel.)

PA Interface:

Notes on PA Interface Implementation:

- There are some surface mount LEDs visible -- these are not used.

- This picture was taken before I added the three PNP inverters for the three PAF signals.

Notes on Performance:

1. DAC rolloff:

The frequency response of Digital to Analog Converters (DACs) is not flat, but rolls off according to the following sin(x)/x formula:

H(f) = sin(πf/fs)/(πf/fs)

Given the FPGA SDR's sampling rate (fs) of 80 Mega-samples/second, then the DAC output will be down 0.5 dB at 14.35 MHz, 1.0 dB at 21.2 MHz, 1.4 dB at 24.7 MHz, and 2.1 dB at 29.7 MHz.

(For more on DAC sin(x)/x rolloff, go here: https://www.maximintegrated.com/en/app-notes/index.mvp/id/3853 or here:

http://www.atx7006.com/articles/dac_frequency_response

2. PA IMD Measurements:

(Click on image to enlarge)

(Click on image to enlarge)

Notes on PA IMD Measurements:

- I'm only going to measure 3rd order IMD, not higher orders.

- The value "% of Max SDR Drive" is the amount of "possible" drive (in terms of voltage level) from the SDR's transmitter that, with this SDR-1000 PA, results in 100 watts out (roughly). Note that the maximum output from the SDR FPGA is 0 dBm (and this drops slightly as frequency increases due to sinx/x rolloff).

- "Power Out" is measured with an LP-100 Digital Vector RF Wattmeter.

- The "Two-Tone Fundamental" is the measured amplitude of one of the two two-tones on the HP 8568B Spectrum Analyzer.

- The "Delta to 3rd Order Spur" is the delta in amplitude from either of the two-tone amplitudes (the value in the previous column) to the 3rd order spur.

- TX IMD, referenced to two-tone PEP power (the latter being 6 dB above either of the two-tone amplitudes).

- Measuring "120 VAC Input Power" from the AC line gives me a rough idea of PA efficiency. (Note that this value also includes power to the FPGA SDR as well as the LP-100 Wattmeter).

- IMD generally worsens as frequency increases except for 160 Meters, which has significantly worse IMD compared to 80 - 15 meters (note that the 120 VAC watts is quite high, too). This might indicate a problem with the 160 meter Low-Pass Filter, for example.

- 100 watts of two-tone PEP power, fed through a 50 dB attenuator, should result in the level of each of the two-tone signals, at the 8568B Spectrum Analyzer, at -6.0 dB. But they aren't -- this error might be due to 8568B calibration error, LP-100 calibration error, the 50 dB attenuator not being exactly 50 dB, or something else. But the measurements are close enough to -6 dBm for my purposes.

(Click on image to enlarge)

For the same reason, I limited the maximum power on 12 meters to about 90 watts.

3. Driver IMD Measurements:

Which functional TX block contributes the most to TX IMD -- the driver or the PA? Let's verify.

Here's the test setup:

(Click on image to enlarge)

(The "Homebrew Directional Coupler" is described here: http://k6jca.blogspot.com/2015/01/building-hf-directional-coupler.html).

And here are the measurements. The Driver's IMD is shown in the very last column.

(Click on image to enlarge)

Clearly, IMD performance is limited by the PA, not the driver, even on 10 meters.

Future Additions:

Some future additions that I plan to incorporate in...the future:

- Fan controller and temperature monitor

- External Speaker on the Front Panel.

- Local controls for stand-alone PA applications

OK. That's it for this blog post!

Background Notes:

SDR Notes: Weaver Modulation and Demodulation

SDR Notes: The Mixer Mathematics of Digital Down Conversion

Posts in this Series:

Part 1: Overview

Part 2: FPGA Modulation and Demodulation

Part 3: Interpolation and Decimation Filters

Part 5: Control Interface, Etc.

Part 9: 50 dB HF RF Power Amplifier

Standard Caveat:

I might have made a mistake in my designs, equations, schematics, models, etc. If anything looks confusing or wrong to you, please feel free to comment below or send me an email.

Also, I will note:

This design and any associated information is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE.

No comments:

Post a Comment