(Part 9 of the series is here: Part 9).

Before I begin, let me again acknowledge Dick Benson, W1QG. Dick is the father of this FPGA SDR design, and although I've made some modifications to the FPGA logic, the underlying architecture and the vast majority of the Simulink implementation is Dick's.

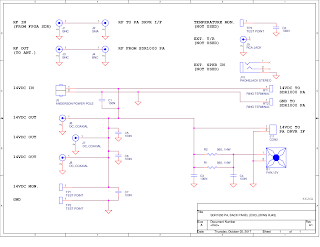

These schematics were drawn using the Lite version of Cadence's Orcad Capture. This is the free version of the program, and it limits a schematic's number of nets to 75 and the number of parts to 60 (limitations which apply if you want to save the design, which I always do).

Because this radio design has many more nets and parts than the 75/60 limit specified by Cadence, I have broken the overall design into smaller "bite size" schematics, each independent of the others and each drawn on a single A-size sheet.

But because I've broken up the design into smaller independent pieces, I can not use Capture's Design Rule Checker to check the overall design for design flaws. Therefore, there is the possibility that errors have crept into the schematics. So be aware!

Schematic:

(Click on image to enlarge)

Schematic Notes:

1. F1, the Corcom 0960-0446 Filter, is the orignal AC Power Inlet plus fuse plus filter that was installed in the HP 37203A unit. Its filtering consists of an 18 nF cap on the Line side of its filter and 465 uH inductors in the Live and in the Neutral AC line wires. You can see its schematic in the image, below.

2. F2 is a Corcom 10VW1 AC Line filter:

3. Ferrite Beads FB1 and FB4 are common-mode chokes, and each consists of a single turn through a Fair-Rite 26354-0002 ferrite core.

4. Ferrite Beads FB2 and FB3 are common-mode chokes on the DC output side of the supply, each consisting of 2 turns around a Fair-Rite 2643102002 ferrite core. (At least I believe they are 2643102002 cores -- they were in a bag marked "43?" in my junk-box. You can see them below, in a shot of the inside of the back panel.)

5. The Power Switch, SW1, is the HP chassis' original power switch.

6. The heart of this supply is a commercially available switching power supply, the MegaWatt S-400-12. At this time, this supply can be purchased via Amazon. Note that Amazon sells other supplies with the same specs and whose case look identical to the MegaWatt supply for much lower prices. Are these switchers equivalent? I have no idea. But I would be suspicious that parts might have been removed (not stuffed) in an effort to get the price down.

Here is a picture of my MegaWatt Switcher:

And inside the MegaWatt switcher:

(If you purchase a less expensive knock-off supply, the the EMI-suppression components might have been removed to reduce cost. You can compare your supply to the image above, in which the EMI suppression components are located in the bottom half of the picture).

Build Notes:

Again, I have used an old HP 37203A "HP-IB Extender" Chassis to house this switching supply.

A view into the top of the chassis. (The hand written note tells me to use a larger screw in that corner of the power supply due to stripped threads -- oops!).

The MegaWatt switcher is mounted onto a non-conductive plexiglass plate. I had earlier noticed, during bench testing, that the FPGA SDR had some in-ham-band EMI spurs when the RF PA was stacked directly on top of the MegaWatt switcher so that the PA's heat-sink fins were in direct electrical contact with the MegaWatt case.

I discovered that if I put a piece of paper between the PA heat-sink and the switcher case so that they no longer had direct electrical and physical contact, the spurs went away.

So clearly there was some sort of unwanted noise path between the PA ground (i.e. heat-sink) and the switcher's case (the supply's AC protective ground) and switcher noise was probably being conducted along the shield of the PA's coaxial cable, and thus appearing as receive spurs.

To ensure that the switcher's protective-ground does not have a direct low-impedance AC connection to the PA ground, I mounted the switcher case on a non-conductive piece of plexiglass and then I fed its protective-ground (its chassis ground) through the same ferrite common-mode chokes (baluns) through which the AC Live and Neutral wires pass (refer to schematic).

And on the DC side, the DC output (both plus and minus sides) pass through another set of ferrite common-mode chokes. Again, to (hopefully) provide a high-impedance path to common-mode switcher noise.

The switcher's internal fan exhausts through the bottom of the HP chassis, and so I've mounted the power supply upside down on the plexiglass plate, with the swither's fan pointed down.

The weather-stripping foam around the fan provides an air seal between the top of the MegaWatt switcher and the HP bottom cover.

I discovered that if I put a piece of paper between the PA heat-sink and the switcher case so that they no longer had direct electrical and physical contact, the spurs went away.

So clearly there was some sort of unwanted noise path between the PA ground (i.e. heat-sink) and the switcher's case (the supply's AC protective ground) and switcher noise was probably being conducted along the shield of the PA's coaxial cable, and thus appearing as receive spurs.

To ensure that the switcher's protective-ground does not have a direct low-impedance AC connection to the PA ground, I mounted the switcher case on a non-conductive piece of plexiglass and then I fed its protective-ground (its chassis ground) through the same ferrite common-mode chokes (baluns) through which the AC Live and Neutral wires pass (refer to schematic).

And on the DC side, the DC output (both plus and minus sides) pass through another set of ferrite common-mode chokes. Again, to (hopefully) provide a high-impedance path to common-mode switcher noise.

The switcher's internal fan exhausts through the bottom of the HP chassis, and so I've mounted the power supply upside down on the plexiglass plate, with the swither's fan pointed down.

The weather-stripping foam around the fan provides an air seal between the top of the MegaWatt switcher and the HP bottom cover.

The back panel. Not much there! The holes provide an air intake path for the MegaWatt switcher's fan.

Here is the FPGA SDR, the HF RF PA, and the 30A Switching Power Supply, stacked:

And finally, for reference, here's the stack wiring:

Other Notes:

1. The MegaWatt switcher's fan is a bit noisy. Some reviews on eHam mention replacing it with a higher quality (quieter) fan. (Or I might home-brew a fan speed controller.)

2. EMI:

As a straight-forward test (relatively), let's take a look at noise on the 14V DC out line.

When I first tried this, I saw:

Not great!

But then I did a bit more poking around (spurred on by Dick, W1QG), and discovered that this noise seemed to be introduced by a ground-loop formed by the switcher and scope Protective Grounds (that is, the two devices are connected via the third wire in the AC mains plug), and when the switcher and the scope are also connected together via the scope probe's ground.

By the way, "ground-loop" might not be the right term for this phenomena.

Anyway, I "broke" the loop by "removing" the scope's AC cord's protective ground wire, using this AC adapter:

(Another way to remove noise such as this is to use two scope probes in differential mode).

With the ground loop broken, there is still a bit of noise, but much less than before. So, let me first establish a scope "baseline" of noise intrinsic to the measurement setup before looking at noise introduced by the switching power supply.

Here's the noise baseline:

Notes on the noise baseline:

Next, I will turn ON the switcher, which will power up the RF PA and the FPGA SDR. The scope probe and its ground are still attached to the switcher's chassis. Here's a shot of the noise now:

When I first tried this, I saw:

Not great!

But then I did a bit more poking around (spurred on by Dick, W1QG), and discovered that this noise seemed to be introduced by a ground-loop formed by the switcher and scope Protective Grounds (that is, the two devices are connected via the third wire in the AC mains plug), and when the switcher and the scope are also connected together via the scope probe's ground.

By the way, "ground-loop" might not be the right term for this phenomena.

Anyway, I "broke" the loop by "removing" the scope's AC cord's protective ground wire, using this AC adapter:

(Another way to remove noise such as this is to use two scope probes in differential mode).

With the ground loop broken, there is still a bit of noise, but much less than before. So, let me first establish a scope "baseline" of noise intrinsic to the measurement setup before looking at noise introduced by the switching power supply.

Here's the noise baseline:

Notes on the noise baseline:

- The Switching supply is OFF.

- The scope signal is AC coupled, so I am just looking at noise, not DC.

- The scope probe ground is attached to the switcher's chassis, as is the scope probe, itself.

- The scope's AC power cord has had its "protective ground" pin floated by using a 3-pin to 2-pin adapter.

Next, I will turn ON the switcher, which will power up the RF PA and the FPGA SDR. The scope probe and its ground are still attached to the switcher's chassis. Here's a shot of the noise now:

No difference that I can see.

Now, let's move the probe over to the 14V DC line while keeping scope probe ground connected to the chassis:

Still not much difference!

But apart from that, not much additional noise.

Let's see how the noise changes if the switcher is sourcing a lot of power -- in other words, when I am transmitting.

If transmitting (3.865 MHz, CW, 100 watts out), the 50-60 KHz component increases significantly, as shown below. Note that the vertical scale has been increased by a factor of 10, from 20mv/div to 200mv/div:

Let's see how the noise changes if the switcher is sourcing a lot of power -- in other words, when I am transmitting.

If transmitting (3.865 MHz, CW, 100 watts out), the 50-60 KHz component increases significantly, as shown below. Note that the vertical scale has been increased by a factor of 10, from 20mv/div to 200mv/div:

EMI comments...

(Click on image to enlarge)

Circuit built and listening tests performed...

The switcher was set to 14.3 VDC out and the linear supply set to 13.6 VDC out. A 50 ohm dummy load (ME-165/G ) was switched into the antenna feed-line, and I tuned in 1 KHz steps (in CW mode) listening for strange noises. (Note that the antenna feed-line is grounded where it exits the shack -- I wanted to maintain this ground connection during this test to see if there was an unwanted ground loop upon which noise would travel along the coax feed-line's shield and by this path introduce noise into the receiver).

The results:

1. I did not hear any spurs generated by the switcher power supply.

OK. That's it for this blog post!

Background Notes:

SDR Notes: Weaver Modulation and Demodulation

SDR Notes: The Mixer Mathematics of Digital Down Conversion

Posts in this Series:

Part 1: Overview

Part 2: FPGA Modulation and Demodulation

Part 3: Interpolation and Decimation Filters

Part 5: Control Interface, Etc.

Part 9: 50 dB HF RF Power Amplifier

Standard Caveat:

I might have made a mistake in my designs, equations, schematics, models, etc. If anything looks confusing or wrong to you, please feel free to comment below or send me an email.

Also, I will note:

This design and any associated information is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE.